In LLVM Git yesterday for next year’s LLVM 22 release the Qualcomm Xqci RISC-V vendor extension is no longer deemed experimental.

Xqci is a Qualcomm extension designed for RISC-V micro-controllers. Xqci fills in gaps of RISC_V functionality around embedded and micro-controller needs for interrupt handling, load/store differences, and various other new instructions. Qualcomm sums up Xqci as:

“This extension contains a lot of new instructions, for a variety of uses from simple bit manipulation instructions to memory accesses with wider offsets, and new branches and jumps.”

With LLVM 20 adding assembler support for this vendor extension and code generation in LLVM 21, for LLVM 22 it’s no longer going to be considered experimental.

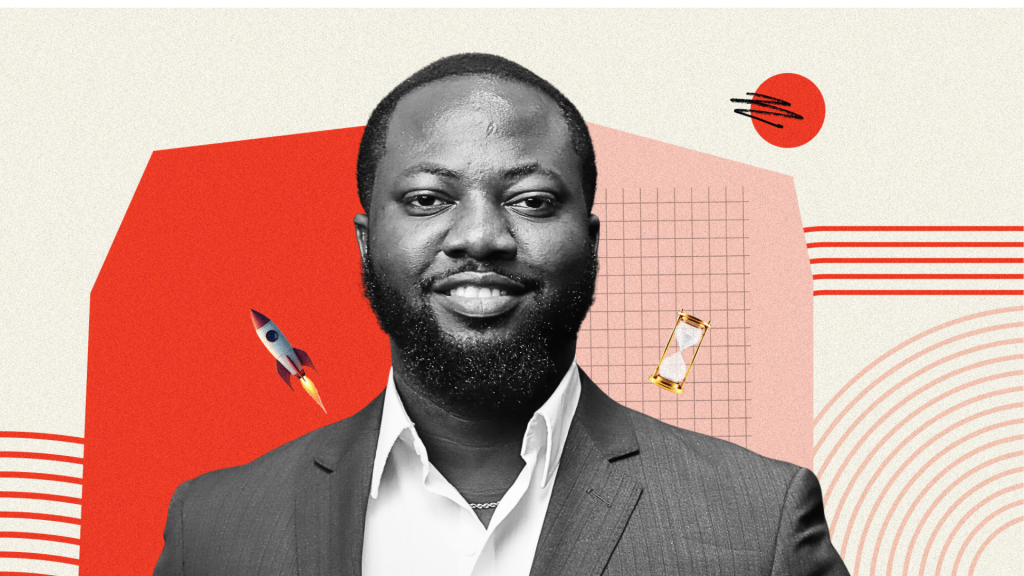

This LLVM commit by Qualcomm engineer Sudharsan Veeravalli promotes this important micro-controller RISC-V extension to being non-experimental.

Qualcomm has been making many RISC-V investments and with their recent acquisition of Ventana it will be interesting to see what new announcement come out of the company in the new year.